안녕하세요. Zynq 7000 TRM 문서를 구글 번역을 올려둡니다.

제가 보기위한 글이지만 참고하세요

문서 : Zynq-7000 SoC Technical Reference Manual (UG585) p226~237

url : https://docs.xilinx.com/v/u/en-US/ug585-Zynq-7000-TRM

Zynq-7000 SoC Technical Reference Manual (UG585)

docs.xilinx.com

7.1 환경

이 장에서는 시스템 수준의 인터럽트 환경과 인터럽트 컨트롤러의 기능에 대해 설명합니다(그림 7-1 참조). PS는 2개의 Cortex-A9 프로세서(CPU)와 GIC pl390 인터럽트 컨트롤러를 활용하는 Arm 아키텍처를 기반으로 합니다. 단일 코어 장치에는 하나의 Cortex-A9 프로세서(CPU)가 포함되고 이중 코어 장치에는 두 개가 포함됩니다. 이 장에서는 듀얼 코어 구성에 대해 설명합니다. 인터럽트 구조는 CPU와 밀접하게 연관되어 있으며 I/O 주변 장치(IOP) 및 프로그래밍 가능 로직(PL)의 인터럽트를 받아들입니다.

이 장에는 다음과 같은 주요 항목이 포함되어 있습니다.

• 개인, 공유 및 소프트웨어 인터럽트

• GIC 기능

• 인터럽트 우선 순위 지정 및 처리

7.1.1 개인, 공유 및 소프트웨어 인터럽트

각 CPU에는 뱅크 레지스터를 사용하여 개인 액세스가 가능한 개인 주변 장치 인터럽트(PPI) 세트가 있습니다.

PPI에는 전역 타이머, 개인 감시 타이머, 개인 타이머 및 PL의 FIQ/IRQ가 포함됩니다.

소프트웨어 생성 인터럽트(SGI)는 하나 또는 두 CPU로 라우팅됩니다. SGI는 일반 인터럽트 컨트롤러(GIC)의 레지스터에 기록하여 생성됩니다. 섹션 7.3 레지스터 개요를 참조하십시오. 공유 주변 장치 인터럽트(SPI)는 PS 및 PL의 다양한 I/O 및 메모리 컨트롤러에서 생성됩니다. CPU 중 하나 또는 둘 다로 라우팅됩니다. PS 주변 장치의 SPI 인터럽트도 PL로 라우팅됩니다.

7.1.2 일반 인터럽트 컨트롤러(GIC)

일반 인터럽트 컨트롤러(GIC)는 PS 및 PL에서 CPU로 전송되는 인터럽트를 관리하기 위한 중앙 집중식 리소스입니다. 컨트롤러는 인터럽트를 활성화, 비활성화, 마스크 및 우선 순위 지정합니다.

CPU 인터페이스가 다음 인터럽트를 수락할 때 프로그래밍된 방식으로 소스를 가져와 선택한 CPU(또는 CPU)로 보냅니다. 또한 컨트롤러는 보안 인식 시스템 구현을 위한 보안 확장을 지원합니다. 컨트롤러는 벡터화되지 않은 Arm 일반 인터럽트 컨트롤러 아키텍처 버전 1.0(GIC v1)을 기반으로 합니다.

레지스터는 인터커넥트에서 일시적인 막힘 또는 기타 병목 현상을 피함으로써 빠른 읽기/쓰기 응답을 위해 CPU 전용 버스를 통해 액세스됩니다. 인터럽트 분배기는 가장 높은 인터럽트 소스를 발송하기 전에 모든 인터럽트 소스를 중앙 집중화합니다.

개별 CPU에 우선 순위를 부여합니다. GIC는 여러 CPU를 대상으로 하는 인터럽트가 한 번에 하나의 CPU에서만 수행될 수 있도록 합니다. 모든 인터럽트 소스는 고유한 인터럽트 ID 번호로 식별됩니다.

모든 인터럽트 소스에는 구성 가능한 자체 우선 순위와 대상 CPU 목록이 있습니다.

7.1.3 재설정 및 시계

인터럽트 컨트롤러는 SLCR에 있는 A9_CPU_RST_CTRL 레지스터의 PERI_RST 비트에 기록함으로써 리셋 서브시스템에 의해 리셋됩니다. 동일한 재설정 신호는 CPU 개인 타이머와 개인 감시 타이머(AWDT)도 재설정합니다. 재설정 시 대기 중이거나 서비스 중인 모든 인터럽트는 무시됩니다.

인터럽트 컨트롤러는 CPU_3x2x 클록(CPU 주파수의 절반)으로 작동합니다.

7.1.4 블록 다이어그램

공유 주변 장치 인터럽트는 PS의 I/O 주변 장치와 PL의 논리를 포함하는 다양한 하위 시스템에서 생성됩니다. 인터럽트 소스는 그림 7-2에 설명되어 있습니다.

7.1.5 CPU 인터럽트 신호 통과

PL의 IRQ/FIQ는 GIC를 통해 PPI#4 및 #1로 라우팅되거나 그림 7-3에 표시된 패스스루 멀티플렉서를 사용하여 GIC를 우회할 수 있습니다. 이 논리는 두 CPU 모두에 대해 인스턴스화됩니다. 통과 모드는 표 7-1에 따라 mpcore.ICCICR 레지스터를 통해 활성화됩니다.

7.2 기능 설명

7.2.1 소프트웨어 생성 인터럽트(SGI)

각 CPU는 소프트웨어 생성 인터럽트(SGI)를 사용하여 자체, 다른 CPU 또는 두 CPU를 모두 인터럽트할 수 있습니다.

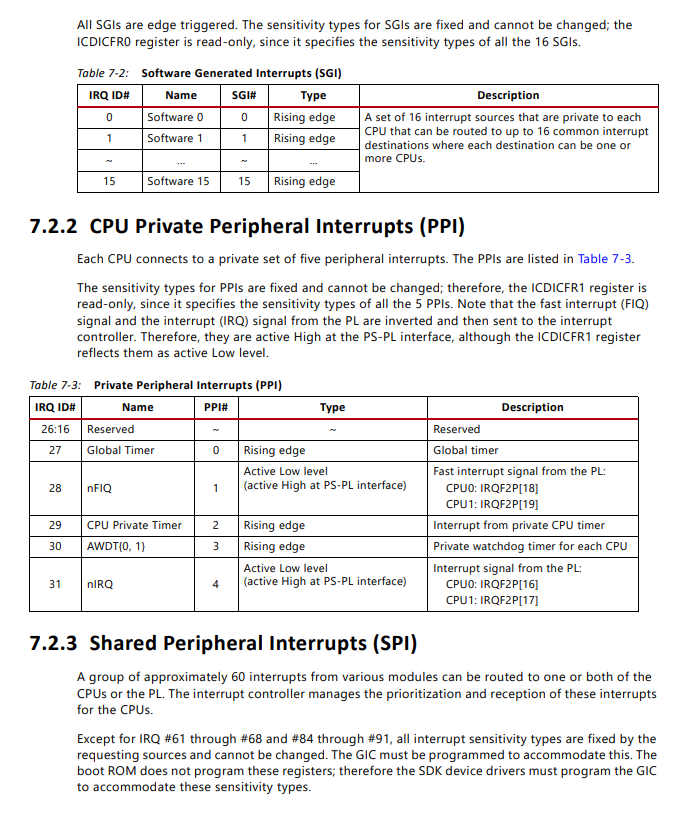

16개의 소프트웨어 생성 인터럽트가 있습니다(표 7-2 참조). SGI는 SGI 인터럽트 번호를 ICDSGIR 레지스터에 기록하고 대상 CPU를 지정하여 생성됩니다. 이 쓰기는 CPU 자체의 전용 버스를 통해 발생합니다. 각 CPU에는 16개의 소프트웨어 생성 인터럽트 중 하나 이상을 생성하는 자체 SGI 레지스터 세트가 있습니다. 인터럽트는 ICCIAR(Interrupt Acknowledge) 레지스터를 읽거나 ICDICPR(Interrupt

Clear-Pending) 등록합니다. 모든 SGI는 에지 트리거됩니다. SGI의 민감도 유형은 고정되어 있으며 변경할 수 없습니다. ICDICFR0 레지스터는 모든 16 SGI의 민감도 유형을 지정하므로 읽기 전용입니다.

7.2.2 CPU PPI(Private Peripheral Interrupt)

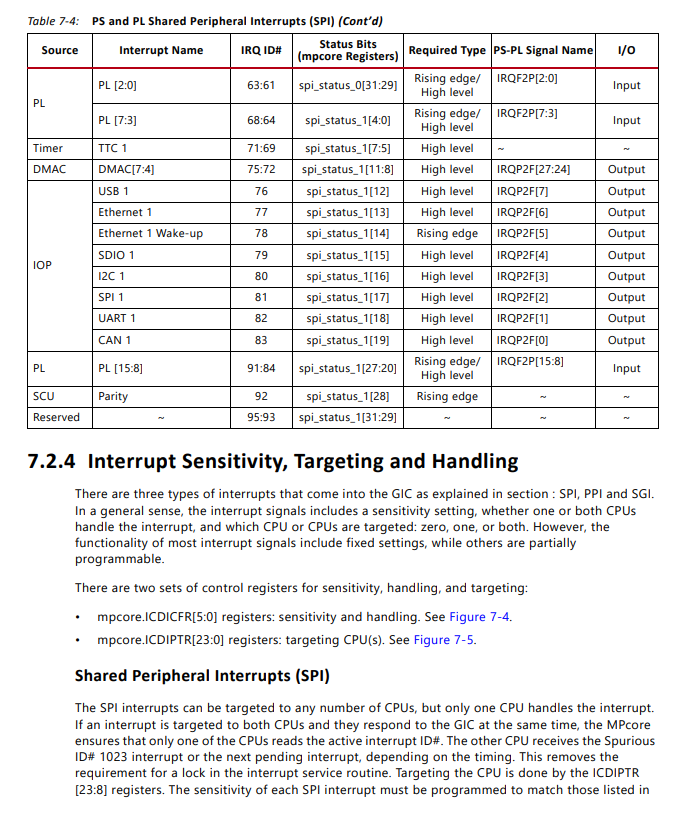

각 CPU는 5개의 주변 장치 인터럽트의 개인 세트에 연결됩니다. PPI는 표 7-3에 나열되어 있습니다.

PPI의 민감도 유형은 고정되어 있으며 변경할 수 없습니다. 따라서 ICDICFR1 레지스터는 모든 5개 PPI의 민감도 유형을 지정하므로 읽기 전용입니다.

PL의 고속 인터럽트(FIQ) 신호와 인터럽트(IRQ) 신호는 반전된 다음 인터럽트 컨트롤러로 전송됩니다. 따라서 ICDICFR1 레지스터가 활성 Low 레벨로 반영하더라도 PS-PL 인터페이스에서 활성 High입니다.

7.2.3 공유 주변 장치 인터럽트(SPI)

다양한 모듈의 약 60개 인터럽트 그룹을 CPU 또는 PL 중 하나 또는 둘 모두로 라우팅할 수 있습니다. 인터럽트 컨트롤러는 CPU에 대한 이러한 인터럽트의 우선 순위 지정 및 수신을 관리합니다. IRQ #61 ~ #68 및 #84 ~ #91을 제외하고 모든 인터럽트 감도 유형은 요청 소스에 의해 고정되며 변경할 수 없습니다. 이를 수용하도록 GIC를 프로그래밍해야 합니다. 부트 ROM은 이러한 레지스터를 프로그래밍하지 않습니다. 따라서 SDK 장치 드라이버는 이러한 민감도 유형을 수용하도록 GIC를 프로그래밍해야 합니다.

수준 민감도 유형의 인터럽트의 경우 요청 소스는 인터럽트가 승인된 후 인터럽트를 지우기 위해 인터럽트 처리기에 대한 메커니즘을 제공해야 합니다. 이 요구 사항은 높은 수준의 감도 유형을 가진 모든 IRQF2P[n](PL에서)에 적용됩니다. 상승 에지 감도 인터럽트의 경우 요청 소스는 GIC가 포착할 수 있을 만큼 충분히 넓은 펄스를 제공해야 합니다. 이것은 일반적으로 최소 2 CPU_2x3x 기간입니다. 이 요구 사항은 상승 에지 감도 유형이 있는 모든 IRQF2P[n](PL에서)에 적용됩니다. ICDICFR2 ~ ICDICFR5 레지스터는 모든 SPI의 인터럽트 유형을 구성합니다. 각 인터럽트에는 민감도 유형 및 처리 모델을 지정하는 2비트 필드가 있습니다.

SPI 인터럽트는 표 7-4에 나열되어 있습니다.

7.2.4 인터럽트 감도, 타겟팅 및 처리

SPI, PPI 및 SGI 섹션에서 설명한 대로 GIC에 들어오는 세 가지 유형의 인터럽트가 있습니다.

일반적으로 인터럽트 신호에는 민감도 설정, 하나 또는 두 CPU가 인터럽트를 처리하는지 여부, 대상 CPU(0, 1 또는 둘 다)가 포함됩니다. 그러나 대부분의 인터럽트 신호의 기능에는 고정된 설정이 포함되며 나머지는 부분적으로 프로그래밍할 수 있습니다.

민감도, 처리 및 타겟팅을 위한 두 세트의 제어 레지스터가 있습니다.

• mpcore.ICDICFR[5:0] 레지스터: 감도 및 처리. 그림 7-4를 참조하십시오.

• mpcore.ICDIPTR[23:0] 레지스터: 대상 CPU. 그림 7-5를 참조하십시오.

SPI(Shared Peripheral Interrupts) SPI 인터럽트는 여러 CPU를 대상으로 할 수 있지만 하나의 CPU만 인터럽트를 처리합니다.

인터럽트가 두 CPU를 대상으로 하고 동시에 GIC에 응답하는 경우 MPcore는 CPU 중 하나만 활성 인터럽트 ID#를 읽도록 합니다. 다른 CPU는 스퓨리어스를 수신합니다.

타이밍에 따라 ID# 1023 인터럽트 또는 다음 보류 중인 인터럽트. 이렇게 하면 인터럽트 서비스 루틴에서 잠금에 대한 요구 사항이 제거됩니다. CPU 대상 지정은 ICDIPTR에 의해 수행됩니다.

[23:8] 레지스터. 각 SPI 인터럽트의 감도는 표 7-4, PS 및 PL SPI(Shared Peripheral Interrupts)에 나열된 것과 일치하도록 프로그래밍해야 합니다. 감도는 다음을 사용하여 프로그래밍됩니다.

ICDICFR [5:2] 레지스터.

개인 주변 장치 인터럽트(PPI)

각 CPU에는 고정된 기능을 가진 별도의 PPI 인터럽트가 있습니다. 이러한 인터럽트의 민감도, 처리 및 타겟팅은 프로그래밍할 수 없습니다. 각 인터럽트는 자체 CPU로만 이동하며 해당 CPU에서 처리합니다. ICDICFR [1] 레지스터는 읽기 전용이며 ICDIPTR [5:2] 레지스터는 기본적으로 예약되어 있습니다.

7.2.5 인터럽트 이벤트 신호 대기(WFI)

CPU는 인터럽트(또는 이벤트) 신호가 생성되기를 기다리는 대기 상태에 들어갈 수 있습니다. PL로 전송되는 인터럽트 대기 신호는 3장 애플리케이션 처리 장치에서 설명합니다.

7.3 레지스터 개요

ICC 및 ICD 레지스터는 pl390 GIC 레지스터 세트의 일부입니다. 60개의 SPI 인터럽트가 있습니다. 이것은 pl390이 지원할 수 있는 것보다 훨씬 적기 때문에 인터럽트 활성화, 상태, 우선 순위 지정이 훨씬 적습니다.

l390에서 가능한 것보다 ICD의 프로세서 대상 레지스터. ICC 및 ICD 레지스터의 요약은 표 7-5에 나열되어 있습니다.

7.3.1 쓰기 방지 잠금

인터럽트 컨트롤러는 중요한 구성 레지스터에 대한 쓰기 액세스를 방지하는 기능을 제공합니다. 이는 APU_CTRL[CFGSDISABLE] 비트에 1을 기록하여 수행됩니다. APU_CTRL 레지스터는 SoC의 시스템 수준 제어 레지스터 세트인 SLCR의 일부입니다. 이는 보안 인터럽트 제어 레지스터에 대한 쓰기 동작을 제어합니다.

7.4 프로그래밍 모델

7.4.1 인터럽트 우선순위

모든 인터럽트 요청(PPI, SGI 및 SPI)에는 고유한 ID 번호가 할당됩니다. 컨트롤러는 ID 번호를 사용하여 중재합니다. 인터럽트 분배기는 각각에 대해 보류 중인 인터럽트 목록을 보유합니다.

CPU, 그런 다음 CPU 인터페이스에 발행하기 전에 우선 순위가 가장 높은 인터럽트를 선택합니다. 동일한 우선 순위의 인터럽트는 가장 낮은 ID를 선택하여 해결됩니다.

우선 순위 지정 논리는 각 CPU에 대해 가장 높은 우선 순위 인터럽트를 동시에 선택할 수 있도록 물리적으로 복제됩니다. 인터럽트 분배기는 인터럽트, 프로세서 및 활성화 정보의 중앙 목록을 보유하고 있으며 CPU에 대한 소프트웨어 인터럽트 트리거를 담당합니다.

SGI 및 PPI 배포자 레지스터는 연결된 각 프로세서에 대해 별도의 복사본을 제공하기 위해 저장됩니다. 하드웨어는 여러 CPU를 대상으로 하는 인터럽트가 한 번에 하나의 CPU에서만 수행될 수 있도록 합니다.

인터럽트 분배기는 보류 중인 가장 높은 인터럽트를 CPU 인터페이스로 전송합니다. 인터럽트가 승인되었다는 정보를 다시 수신하고 인터럽트의 상태를 변경할 수 있습니다.

해당 인터럽트. 인터럽트를 승인한 CPU만이 해당 인터럽트를 종료할 수 있습니다.

7.4.2 인터럽트 처리

IRQ 라인이 선언 해제될 때 보류 중인 인터럽트에 대한 GIC의 응답은 Arm 문서 IHI0048B_gic_architecture_specification.pdf(부록 A, 추가 리소스 참조)에 설명되어 있습니다. 섹션 3.2.4의 추가 정보와 함께 섹션 1.4.2의 참고를 참조하십시오. 인터럽트가 GIC에서 보류 중이고 IRQ가 선언 해제되면 GIC의 인터럽트는 비활성화되고 CPU는 이를 인식하지 못합니다.

GIC에서 인터럽트가 활성화되면(CPU 인터페이스가 인터럽트를 승인했기 때문에) 소프트웨어 ISR은 먼저 GIC 레지스터를 확인한 다음 I/O 주변 장치 인터럽트 상태 레지스터를 폴링하여 원인을 결정합니다.

7.4.3 Arm 프로그래밍 주제

Arm GIC 아키텍처 사양에는 다음과 같은 프로그래밍 주제가 포함됩니다.

• GIC 레지스터 액세스

• 분배기 및 CPU 인터페이스

• GIC 보안 확장의 영향

• PU 인터페이스 레지스터

• 컨트롤러 상태 유지 및 복원

7.4.4 레거시 인터럽트 및 보안 확장

레거시 인터럽트(IRQ, FIQ)가 사용되고 인터럽트 처리기가 보안 모드(ICCICR[AckCtl]=1을 통해)에서 IRQ 및 FIQ 모두에 액세스하는 경우 인터럽트 ID를 읽을 때 경쟁 조건이 가끔 발생합니다. 또한 IRQ 핸들러에서 FIQ ID를 볼 위험이 있습니다. GIC는 핸들러 유형이 아니라 핸들러가 읽는 보안 상태만 알고 있기 때문입니다.

두 가지 실행 가능한 솔루션이 있습니다.

• 재진입 IRQ 처리기에만 IRQ 신호를 보내고 GIC의 선점 기능을 사용합니다.

• ICCICR[AckCtl]=0과 함께 FIQ 및 IRQ를 사용하고 TLB 테이블을 사용하여 비보안 환경에서 IRQ를 처리합니다.

모드로 전환하고 보안 모드에서 FIQ를 처리합니다.

'임베디드' 카테고리의 다른 글

| [임베디드-eclipse]Eclipse CDT 컴파일 옵션 설정 (0) | 2023.01.09 |

|---|---|

| [임베디드-FreeRTOS]Task 프로파일링 - Run Time Statistics(런타임 통계) (0) | 2022.12.28 |

| [임베디드-FreeRTOS]HALT : Task [name] overflowed its stack. Test [ProjectName] 오류 (0) | 2022.12.28 |

| [임베디드]ARM 아키텍처 (0) | 2022.12.27 |